## PATENT ABSTRACTS OF JAPAN

(11)Publication number:

2001-250912

(43)Date of publication of application: 14.09.2001

(51)Int.Cl.

H01L 25/07 H01L 23/52

(21)Application number : 2000-062298

(22) Date of filing:

07.03.2000

(71)Applicant:

SEIKO EPSON CORP

(72)Inventor:

MATSUI KUNIYASU

### [54] SEMICONDUCTOR DEVICE AND ITS MANUFACTURING METHOD AND ELECTRONIC EQUIPMENT

57) Abstract:

PROBLEM TO BE SOLVED: To provide a semiconductor device and its manufacturing nethod and electronic components that can electrically connect a laminated semiconductor chip to an external device or the like without using any auxiliary means such as an interposer, and can adopt the configuration regardless of the size of the aminated semiconductor chip.

SOLUTION: A through hole 12 is formed in semiconductor chips 10a, 10b, 10c, and 10d. Then, a conductive film 16 made of gold is formed on the inner- periphery surface of the through hole 12 and near an opening part. In addition, the inside of the through hole 14n 12 is filled with resin 18, thus electrically connecting an electrode 14 of the semiconductor chip 10d to the conductive film 16, and hence electrically connecting the external device that is provided at the side of the semiconductor chip 10a and is not shown in a figure to the semiconductor chip 10d.

**EGAL STATUS**

Date of request for examination]

Date of sending the examiner's decision of rejection]

Kind of final disposal of application other than the examiner's

decision of rejection or application converted registration]

Date of final disposal for application]

Patent number]

Date of registration]

Number of appeal against examiner's decision of rejection]

Date of requesting appeal against examiner's decision of ejection]

Date of extinction of right]

08.03.2004

withdrawal

05.01.2006

THIS PAGE BLANK (USPTO)

JPO and NCIPI are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely.

2.\*\*\*\* shows the word which can not be translated.

3.In the drawings, any words are not translated.

### **CLAIMS**

[Claim(s)]

[Claim 1] The manufacture approach of the semiconductor device characterized by having at least the 1st process which forms a through tube in said semiconductor chip by which the laminating was carried out in the manufacture approach of the semiconductor device which comes to carry out the laminating of two or more semiconductor chips, the 2nd process which forms the electric conduction film by electroless deposition on the inner skin of said through tube, and the 3rd process filled up with resin in said through tube.

[Claim 2] The manufacture approach of the semiconductor device according to claim 1 characterized by being filled up with the resin containing an electric conduction particle as resin with which it is filled up in said through tube.

[Claim 3] The manufacture approach of the semiconductor device according to claim 1 characterized by forming said electric conduction film also near the opening of said through tube.

[Claim 4] The manufacture approach of the semiconductor device according to claim 1 to 3 characterized by forming a through tube in some electrode pads formed in the active element forming face of said semiconductor chip in said 1st process.

[Claim 5] The manufacture approach of the semiconductor device according to claim 1 to 4 characterized by having the process which forms an insulator layer between said 1st process and said 2nd process at the inner skin of said through tube.

[Claim 6] Said 2nd process is the manufacture approach of the semiconductor device according to claim 1 to 5 characterized by including the process which prepares a photoresist in fields other than the field which forms said electric conduction film of said said semiconductor chip by which the laminating was carried out, the process which makes a catalyst nucleus adhere to the field which forms said electric conduction film, and the process which carries out the plating bath of said said semiconductor chip by which the laminating was carried out.

[Claim 7] The manufacture approach of the semiconductor device according to claim 1 to 6 characterized by using electrodeposted resin in said 3rd process as resin with which it is filled up in a through tube.

[Claim 8] The semiconductor device characterized by coming to be manufactured by the manufacture approach of a semiconductor device according to claim 1 to 7.

[Claim 9] Electronic equipment characterized by coming to have a semiconductor device according to claim 8.

JPO and NCIPI are not responsible for any damages caused by the use of this translation.

1. This document has been translated by computer. So the translation may not reflect the original precisely.

2.\*\*\*\* shows the word which can not be translated.

3.In the drawings, any words are not translated.

### **DETAILED DESCRIPTION**

[Detailed Description of the Invention]

[0001]

[Field of the Invention] This invention relates to a semiconductor device, its manufacture approach, and electronic equipment, especially relates to a suitable thing to carry out the laminating of two or more semiconductor chips, and use them.

[0002]

[Description of the Prior Art] In the field of a semiconductor device, many things which prepare two or more semiconductor chips in a single package for the purpose of the miniaturization of a semiconductor device and lightweight-izing in recent years and which prepare especially each semiconductor chip in a laminating condition have been developed. Such a semiconductor device is called the multi chip package (MCP) or the multi chip module (MCM). Invention of JP,62-158840,U is mentioned as a concrete example of such equipment. That is, in a single ceramic package, the laminating of two or more chips is carried out, and the electrode of each chip is connected with a wire. Moreover, while mounting a semiconductor chip in the wiring substrate called INTAPOZA like invention of JP,11-135711,A as another example and connecting INTAPOZA mutually, a laminating is carried out and it considers as a single semiconductor device.

[Problem(s) to be Solved by the Invention] However, in invention of JP,62–158840,U, since a wire will be allotted to the perimeter of a semiconductor chip for a large number, the volume of the semiconductor device which has the configuration concerned will be made big beyond the need. Moreover, when the magnitude of the semiconductor chip by which a laminating is carried out is abbreviation identitas, since it will be hidden by the electrode with the semiconductor chip located in a high order, things other than the semiconductor chip located in the topmost part become difficult [bonding]. furthermore, invention of JP,11–135711,A — setting — abbreviation — although it can perform easily carrying out the laminating of the semiconductor chip of the same magnitude, and considering as a single semiconductor device, while mounting each semiconductor chip in INTAPOZA, in order to secure the electrical installation between INTAPOZA, a production process far more complicated than invention of JP,62–158840,U will be required.

[0004] Then, this invention aims at offering the semiconductor device which can adopt the configuration concerned regardless of the magnitude of the semiconductor chip by which a laminating is carried out, its manufacture approach, and electronic equipment while it can connect an external device etc. with the semiconductor chip by which the laminating was carried out electrically, without having been made in order to cancel the fault of the above mentioned conventional technique, and using supplementary means, such as INTAPOZA.

[Means for Solving the Problem] Then, this invention shall be characterized by having at least the 1st process which forms a through tube in said semiconductor chip by which the laminating was carried out, the 2nd process which forms the electric conduction film by electroless deposition on the inner skin of said through tube, and the 3rd process filled up with resin in said through tube in the manufacture approach of the semiconductor device which comes to carry out the laminating of two or more semiconductor chips, in order to attain the above-mentioned purpose.

[0006] Thus, in constituted this invention, it can perform simply forming an electric conduction means in the interior of the through tube formed in the semiconductor chip by which the laminating was carried out. Moreover, in order to prepare resin in the interior of a through tube, dependability increases with the resin with which the inside is filled up that the electric conduction film itself should just be extent which can take a flow. By using the resin which contained the electric conduction particle in the resin with which the interior is furthermore filled up, the dependability of electrical installation improves further.

[0007] Moreover, in the manufacture approach of the above-mentioned semiconductor device, it shall be characterized by here where said electric conduction film is formed also near the opening of said through tube.

[0008] Thus, in constituted this invention, since the electric conduction film formed near the opening of a through tube contributes to electrical installation with wiring, a terminal, etc. of an external device, the dependability of electrical installation with the external device concerned increases. [0009] Moreover, in the manufacture approach of the above-mentioned semiconductor device, it shall be characterized by forming a through tube so that some electrode pads formed in the active element forming face of said semiconductor chip may be drilled in said 1st process.

[0010] Thus, in constituted this invention, since an electrode pad and the electric conduction film are connected electrically, if wiring, a terminal, etc. of an external device are connected to the electric conduction film or the electrodeposted resin prepared near opening of a through tube, it can perform easily connecting electrically each semiconductor chip by which the laminating was carried out to the external device concerned.

[0011] Moreover, in the manufacture approach of the above-mentioned semiconductor device, it shall be characterized by having the process which forms an insulator layer between said 1st process and said 2nd process at the inner skin of said through tube.

[0012] Thus, in constituted this invention, since each semiconductor chip and electric conduction film by which the laminating was carried out are insulated by the insulator layer, the electric conduction film concerned can be used as contact unrelated to electrical installation with the semiconductor chip concerned.

[0013] Moreover, in the manufacture approach of the above-mentioned semiconductor device, said 2nd process shall be characterized by to include the process which prepares a photoresist in fields other than the field which forms said electric conduction film of said said semiconductor chip by which the laminating was carried out, the process which makes a catalyst nucleus adhere to the field which forms said electric conduction film, and the process which carries out the plating bath of said said semiconductor chip by which the laminating was carried out.

[0014] Thus, in constituted this invention, since the electric conduction film is formed by electroless deposition, it can perform easily forming the electric conduction film in the interior of a through tube.

[0015] Moreover, in the manufacture approach of the above-mentioned semiconductor device, it made to use electrodeposted resin into that by which it is characterized in said 3rd process as resin with which it is filled up in a through tube. Thus, in constituted this invention, resin can be formed alternatively and easily in a through tube in a short time.

[0016] Furthermore, in a semiconductor device, it shall be characterized by above either coming to be manufactured by the manufacture approach of the semiconductor device a publication.

[0017] Thus, in constituted this invention, since a wire etc. becomes unnecessary securing the electric flow of semiconductor chips by which the laminating was carried out, it can perform attaining the miniaturization of a semiconductor device easily.

[0018] It shall add and shall be characterized by coming to have the above-mentioned semiconductor device in electronic equipment.

[0019] Thus, in constituted this invention, since the semiconductor device miniaturized conventionally can be used, it can perform attaining the miniaturization of the electronic equipment itself easily.

[0020]

[Embodiment of the Invention] Below, it explains at a detail, referring to an accompanying drawing about the gestalt of suitable operation of the semiconductor device concerning this invention, its manufacture approach, and electronic equipment.

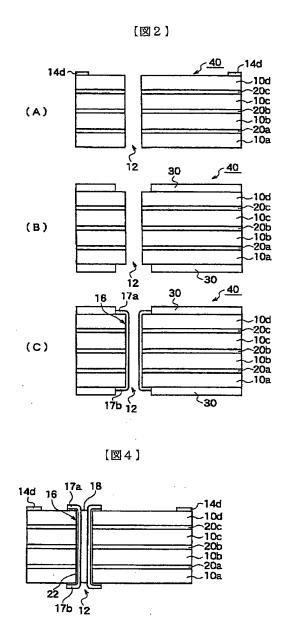

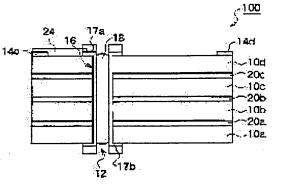

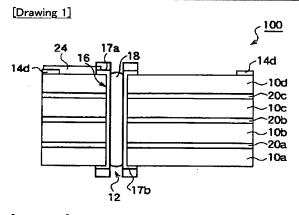

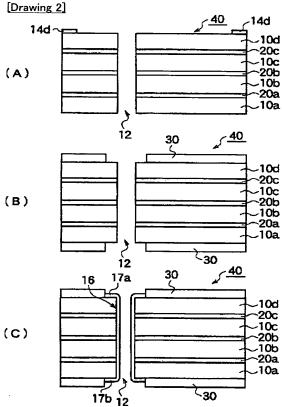

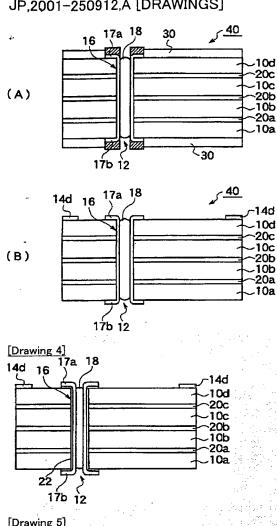

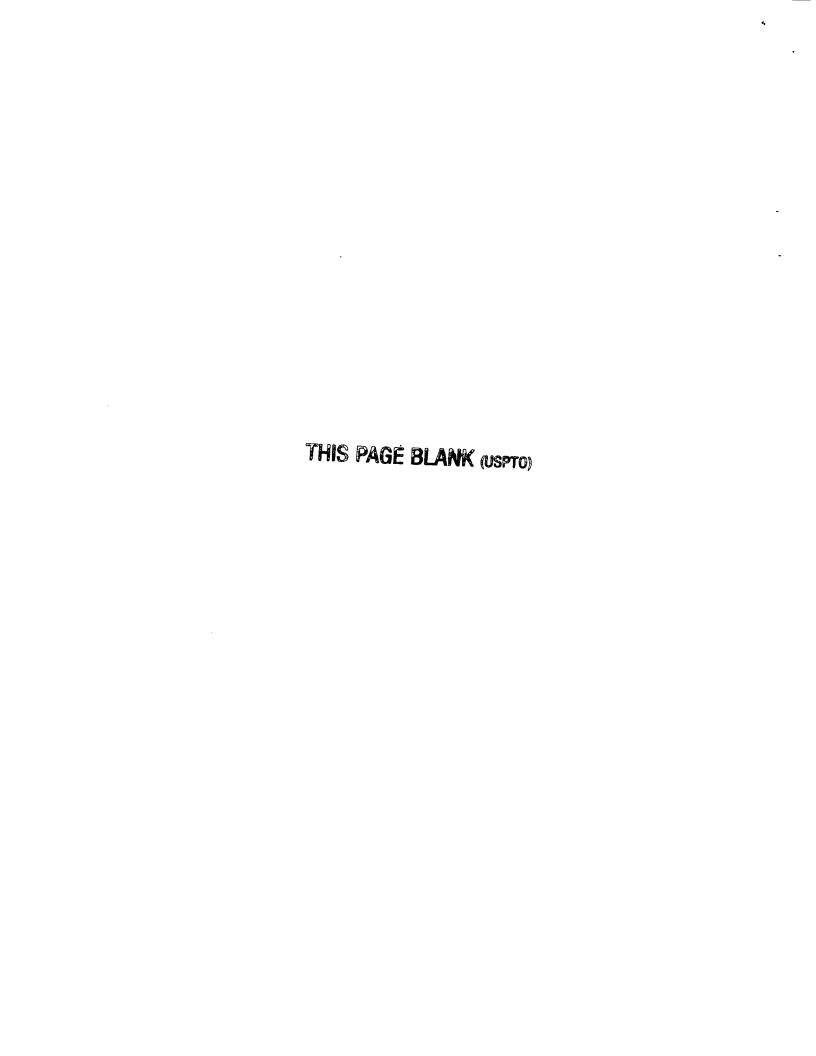

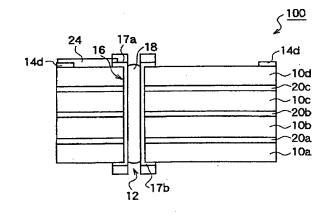

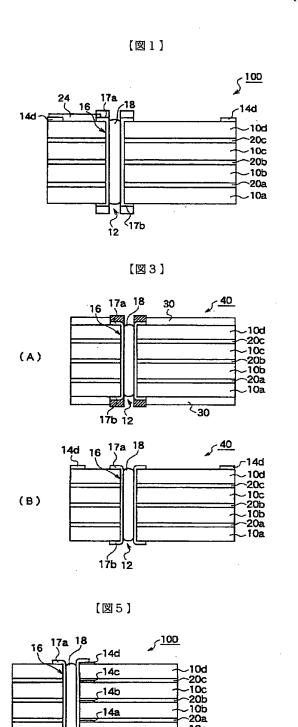

[0021] <u>Drawing 1</u> is the sectional view showing the outline of the semiconductor device concerning the gestalt of operation of the 1st of this invention. Moreover, <u>drawing 2</u> is a sectional view (1) explaining the production process of the semiconductor device concerning the gestalt of operation of the 1st of this invention. Moreover, <u>drawing 3</u> is a sectional view (2) explaining the production process of the semiconductor device concerning the gestalt of operation of the 1st of this invention. Moreover, <u>drawing 4</u> is the sectional view showing the outline of the semiconductor device concerning the gestalt of operation of the 2nd of this invention. Moreover, <u>drawing 5</u> is the sectional view showing the outline of the semiconductor device concerning the gestalt of operation of the 3rd of this invention.

[0022] It explains based on semiconductor device \*\*\*\*\*\* drawing 1 concerning the gestalt of operation of this invention. The semiconductor device 100 concerning the gestalt of this operation is carrying out the laminating of the semiconductor chips 10a, 10b, 10c, and 10d, where an active element forming face (it considers as an active side hereafter) is arranged in this direction. The semiconductor chips 10a, 10b, 10c, and 10d by which the laminating was carried out are pasted up with the adhesives 20a, 20b, and 20c which intervene among these semiconductor chips.

[0023] Moreover, the through tube 12 which penetrates these in the direction of a laminating is formed in semiconductor chips 10a, 10b, 10c, and 10d. The electric conduction film 16 is formed in the inner skin of a through tube 12. The electric conduction film 16 is formed bygold (Au). In addition, about the formation approach, it mentions later. Furthermore, the edges 17a and 17b of the electric conduction film 16 are exposed outside from the through tube 12. It adds and the through tube 12 interior is filled up with resin 18. Resin 18 is acrylic resin, uses cation mold acrylic electrodeposition resin, and is formed by the electrodeposted method.

[0024] According to the gestalt of operation of this invention explained above, if the terminal of an external device etc. is connected to electrode pad 14d in semiconductor chips [ 10a, 10b, 10c, and 10d ] one of fields, the electric conduction film 16 can make connection to the substrate in which a role of contact was prepared sure enough in the field of the semiconductor chips [ 10a, 10b, 10c, and 10d ] opposite side. Therefore, it becomes possible to, connect electrically electrically the external device and 10d of semiconductor chips which were prepared in the semiconductor chip 10a side by connecting with a conductor 24 and which are not illustrated electrode pad 14d formed in 10d of semiconductor chips, and the electric conduction film 16 for example. In addition, it is desirable to make connection between electrode pad 14d and the electric conduction film 16 with tin, a tin alloy, etc.

[0025] In addition, the number of the semiconductor chip by which a laminating is carried out is not restricted to four pieces, and is good as for other numbers. Moreover, the magnitude of the semiconductor chip by which a laminating is carried out may differ, respectively. Moreover, a through tube 12 may be altogether formed two or more corresponding to an electrode pad, if the circuit of each semiconductor chip by which a laminating is carried out etc. is not spoiled. Furthermore, a heat sink may be prepared among semiconductor chips 10a, 10b, 10c, and 10d. In addition, these things are applicable also to the gestalt of other operations.

[0026] Moreover, resin 18 does not need to be completely filled up with the through tube 12, and should just be prepared possible [ the terminal of an external device, etc. and connection]. Moreover, resin 18 may be formed on 17a and 17b, when not using the edge of the electric conduction film 16 for electrical installation. Furthermore, the electric conduction film 16 is formed withgold, and also it may be formed with alloys, such as nickel (nickel), copper (Cu), and nickel-gold (nickel-Au) and nickel-golden-copper (nickel-Au-Cu). In addition, these things are applicable also to the gestalt of other operations.

[0027] It is desirable to add and to prepare the insulator layer for protecting the active side concerned on a semiconductor chips [ 10a, 10b, 10c, and 10d ] active side. Specifically, it is suitable to prepare silicon oxide (SiO2) and a silicon nitride (SiN) as an insulator layer. In addition, this insulator layer should just form a thing which is formed in a semi-conductor wafer production process and which is mentioned later in a semi-conductor wafer manufacture phase. Moreover, the semi-conductor wafer was carried out after dividing into each semiconductor chip, and it may be prepared. Furthermore, an insulator layer may be formed in semiconductor chips [ 10a 10b, 10c, and 10d ] a side face and a rear face by approaches, such as post processing, for example, potting, vacuum evaporationo, and a transfer mold. In addition, these things are applicable also to the gestalt of other operations.

[0028] Moreover, in order to make into a positive thing the electric insulation with the metal wiring layer etc. and the electric conduction film 16 which were formed in semiconductor chips 10a, 10b, 10c, and 10d like the semiconductor device concerning the gestalt of operation of the 2nd of this invention, it is desirable to form an insulator layer 22. That is, as shown in <u>drawing 4</u>, first, an insulator layer 22 is formed in the inner skin of a through tube 12, on it, the laminating of the electric conduction film 16 shall be carried out, and it shall be prepared. If it does in this way, the electric insulation with the electric conduction film 16 and the semiconductor chips [ 10a, 10b 10c, and 10d ] metal wiring layer which is not illustrated can be aimed at certainly.

[0029] In addition, as an insulator layer 22, silicon oxide (SiO2) and a silicon nitride (SiN) are suitable. Furthermore, organic compound insulators, such as polyimide, may be formed. In addition, the formation approach is good by any approach to heat-treat a CVD method and semiconductor chips 10a, 10b, 10c, and 10d in the elevated-temperature ambient atmosphere containing oxygen, to oxidize the part exposed to the inner skin of the connection hole 18, and to form an oxide film etc.

[0030] Next, the manufacture approach of the semiconductor device concerning the gestalt of operation of this invention is explained.

[0031] First, as shown in <u>drawing 2</u> (A), the semi-conductor wafer 40 which finished the process of a semiconductor chip is pasted up in the state of a laminating, a laser beam is irradiated to the part which forms a through tube, and a through tube 12 is formed. In addition, the exposure of a laser beam must be carefully performed so that damage on punching an active element etc. may not be done.

[0032] In addition, a through tube 12 is good also as what is prepared by etching of the sentiment method or the dry cleaning method. Although punching takes time amount rather than the approach using a laser beam when etching by the dry cleaning method, the dry area of the inner skin of a through tube 12 is small. What is necessary is just to make it the approach by which wet etching used alkali solutions, such as KOH, and dry etching used the etching gas of CF4 grade, the approach using the plasma, etc. use what is used by silicon processing as the concrete etching approach.

[0033] Next, as shown in drawing 2 (B), the part which applies a photoresist to semiconductor chips [ by which the laminating was carried out / 10a 10b, 10c, and 10d ] both sides, forms the photoresist film 30 in them, and prepares the electric conduction film in them at a back process is removed.

[0034] Next, as shown in drawing 2 (C), golden electroless deposition is performed to semiconductor chips [ by which the laminating was carried out / 10a 10b, 10c, and 10d ] both sides, and the electric conduction film 16 is formed in them.

[0035] Continuously, as shown in drawing 3 (A), acrylic resin is formed on the electric conduction film 16 using electrodeposted resin. At this time, electrodeposted resin is made not to be formed by a resist etc. beforehand about a part for the terminal area which needs to take an external device and electrical installation behind.

[0036] Next, if a through tube 12 is filled up with electrodeposted resin 18 as shown in <u>drawing 3</u> (B), the photoresist film 30 will be removed. [0037] With the above procedure, the semiconductor device concerning the gestalt of operation of this invention can be manufactured. In addition, in the semiconductor device concerning the gestalt of the 2nd operation shown in <u>drawing 4</u>, after formation of a through tube, an insulator layer 22 is formed by the above-mentioned approach, and the electric conduction film 16 is formed after that. Moreover, it may be difficult to deposit a metal depending on the quality of the material of an insulator layer 22, and to adhere by electroless deposition, on it. In such a case, before the process of the electroless deposition shown in <u>drawing 2</u> (C), the palladium colloidal solution is permeated in semiconductor chips 10a, 10b, 10c, and 10d, and processing which makes palladium adhere to the part which forms the electric conduction film is performed. If this processing is performed, it can

perform easily palladium serving as a catalyst nucleus and forming the electric conduction film on an insulator layer 22.

[0038] Next, the semiconductor device concerning the gestalt of operation of this invention is explained based on <u>drawing 5</u>. The semiconductor device 100 concerning the gestalt of this operation is carrying out the laminating of the field in which each electrode pad 14a, 14b, 14c, and 14d was formed for semiconductor chips 10a, 10b, 10c, and 10d in the condition of having arranged in this direction. The electrode pads 14a, 14b, 14c, and 14d are connected to the circuit which was formed in semiconductor chips 10a, 10b, 10c, and 10d, respectively and which is not illustrated. In addition, Adhesives 10a, 10b, and 10c, the electric conduction film 16, and resin 18 are the same configurations as the thing concerning the gestalt of the 1st operation, and resin 18 is using acrylic electrodeposition resin.

[0039] If the terminal of an external device etc. is connected to either of the edges 17a and 17b of the electric conduction film 16 according to the gestalt of operation of this invention explained above, it will connect with the semiconductor chips [ 10a, 10b, 10c, and 10d ] electrode pads 14a, 14b, 14c, and 14d through the electric conduction film 16. Therefore, regardless of the magnitude of the semiconductor chip by which a laminating is carried out, the semiconductor chip and external device by which the laminating was carried out are electrically connectable. Moreover, a supplementary means like INTAPOZA is not needed.

[0040] In addition, in order to secure certainly an electric flow with the electrode pads 14a, 14b, and 14c and the electric conduction film 16, electric conduction material, such as tin and a tin system alloy, is prepared on the electrode pads 14a and 14b and 14c, it combines with the electrode pads 14a, 14b, and 14c, and the electric conduction film 16 and this electric conduction material may be made to be connected. Furthermore, as long as the electrode pads 14a, 14b, 14c, and 14d are generally used [ copper / (aluminum-Si-Cu) / aluminum (aluminum) and aluminum-silicon (aluminum-Si) and copper (Cu) aluminum-silicon-] as the electrode and wiring of a semiconductor chip, you may be the thing of what kind of the quality of the material-furthermore, electrode pad 14d — a top — the electric conduction film 16 — \*\* — it is desirable to form metal layers (for example, Ti-W, Pt-Au, nickel, Cu-Au, etc.) which are generally known as an undershirt bump metal so that it can connect stably.

[0041] As stated above, the interior is penetrated, the semiconductor device 100 concerning the gestalt of each operation of this invention can plan electrical installation of a peripheral device, and neither a wire nor INTAPOZA needs to be used for it. Moreover, since only the part which prepares neither a wire nor INTAPOZA can be used and contraction—ization of the component—side product of a semiconductor device can be attained, if this semiconductor device 100 is mounted in electronic equipment, the miniaturization of the electrical machinery and apparatus itself can be attained. [0042]

[Effect of the Invention] In the manufacture approach of the semiconductor device which comes to carry out the laminating of two or more semiconductor chips according to this invention as explained above The 1st process which forms a through tube in said semiconductor chip by which the laminating was carried out. Since it is considering as the configuration which has at least the 2nd process which forms the electric conduction film by electroless deposition on the inner skin of said through tube, and the 3rd process which prepares resin with conductivity in said through tube, Semiconductor chips and an external device with a semiconductor chip are electrically connectable through the through tube of the semiconductor chip by which the laminating was carried out. Moreover, since electric connection can be made through supplementary means, such as a wire and INTAPOZA, while contributing also to the miniaturization of a semiconductor device, it contributes also to the cost cut of a semiconductor device remarkably.

JPO and NCIPI are not responsible for any damages caused by the use of this translation.

- 1. This document has been translated by computer. So the translation may not reflect the original precisely.

- 2.\*\*\*\* shows the word which can not be translated.

- 3.In the drawings, any words are not translated. .

### DESCRIPTION OF DRAWINGS

[Brief Description of the Drawings]

[Drawing 1] It is the sectional view showing the outline of the semiconductor device concerning the gestalt of operation of the 1st of this invention. [Drawing 2] It is a sectional view (1) explaining the production process of the semiconductor device concerning the gestalt of operation of the 1st of

[Drawing 3] It is a sectional view (2) explaining the production process of the semiconductor device concerning the gestalt of operation of the 1st of this invention.

[Drawing 4] It is the sectional view showing the outline of the semiconductor device concerning the gestalt of operation of the 2nd of this invention. [Drawing 5] It is the sectional view showing the outline of the semiconductor device concerning the gestalt of operation of the 3rd of this invention. [Description of Notations]

- 10a ..... Semiconductor chip

- 10b ..... Semiconductor chip

- 10c ..... Semiconductor chip

- 10d ..... Semiconductor chip

- 12 ..... Through tube

- 14a ..... Electrode pad

- 14b ..... Electrode pad

- 14c ..... Electrode pad

- 14d ..... Electrode pad

- 16 ..... Electric conduction film

- 17a ..... Edge

- 17b ..... Edge

- 18 ..... Electrodeposted resin

- 20a ..... Adhesives

- 20b ..... Adhesives

- 20c ..... Adhesives

- 22 ..... Insulator layer

- 24 ..... electric a conductor

- 30 ..... Photoresist film

- 40 ..... Semi-conductor wafer which carried out the laminating

- 100 ..... Semiconductor device

JPO and NCIPI are not responsible for any damages caused by the use of this translation.

- 1. This document has been translated by computer. So the translation may not reflect the original precisely.

- 2.\*\*\*\* shows the word which can not be translated.

- 3.In the drawings, any words are not translated.

### **DRAWINGS**

[Drawing 3]

## (19) 日本国特許庁 (JP)

# (12) 公開特許公報(A)

(11)特許出願公開番号 特開2001-250912 (P2001-250912A)

(43)公開日 平成13年9月14日(2001.9.14)

(51) Int.Cl.7

識別記号

FΙ

テーマコート\*(参考)

H01L 25/07 23/52 H01L 25/04

В

23/52

С

## 審査請求 未請求 請求項の数9 OL (全 6 頁)

(21)出願番号

特願2000-62298(P2000-62298)

(22)出願日

平成12年3月7日(2000.3.7)

(71)出願人 000002369

セイコーエプソン株式会社

東京都新宿区西新宿2丁目4番1号

(72)発明者 松井 邦容

長野県諏訪市大和3丁目3番5号 セイコ

ーエプソン株式会社内

(74)代理人 100093388

弁理士 鈴木 喜三郎 (外2名)

## (54) 【発明の名称】 半導体装置およびその製造方法ならびに電子機器

### (57)【要約】

【課題】 インターボーザなどの補助的手段を用いることなく、積層された半導体チップと外部装置等とを電気的に接続することが可能であるとともに、当該構成を積層される半導体チップの大きさに関係なく採用できる半導体装置およびその製造方法ならびに電子機器を提供すること。

【解決手段】 半導体チップ10a、10b、10c、10 dに貫通孔12を形成する。そして、貫通孔12の内周面と開□部の近傍に金による導電膜16を形成する。さらに、貫通孔12内部に樹脂18を充填する。このような構成にすれば、半導体チップ10dの電極14と導電膜16を電気的に接続すれば、半導体チップ10a側に設けられた図示しない外部装置と半導体チップ10dとを電気的に接続することが可能になる。

【特許請求の範囲】

【請求項1】 半導体チップを複数個積層してなる半導 体装置の製造方法において、

複数個積層された前記半導体チップに貫通孔を形成する 第1の工程と

前記貫通孔の内周面上に無電解メッキにより導電膜を形 成する第2の工程と、

前記貫通孔内に樹脂を充填する第3の工程と、を少なく とも有することを特徴とする半導体装置の製造方法。

電粒子を含んだ樹脂を充填することを特徴とする請求項 1 に記載の半導体装置の製造方法。

【請求項3】 前記導電膜を前記貫通孔の開口部の近傍 にも形成することを特徴とする請求項1に記載の半導体 装置の製造方法。

【請求項4】 前記第1の工程において、前記半導体チ ップの能動素子形成面に形成された電極バッドの一部に 貫通孔を形成することを特徴とする請求項1ないし請求 項3のいずれかに記載の半導体装置の製造方法。

【請求項5】 前記第1の工程と前記第2の工程との間 に、前記貫通孔の内周面に絶縁膜を形成する工程を有す ることを特徴とする請求項1ないし請求項4のいずれか に記載の半導体装置の製造方法。

【請求項6】 前記第2の工程は、

前記複数個積層された前記半導体チップの、前記導電膜 を形成する領域以外の領域にフォトレジストを設ける工 程と、

前記導電膜を形成する領域に触媒核を付着させる工程

前記複数個積層された前記半導体チップをメッキ浴する 工程と、を含むことを特徴とする請求項1ないし請求項 5のいずれかに記載の半導体装置の製造方法。

【請求項7】 前記第3の工程において、貫通孔内に充 填する樹脂として、電着樹脂を用いることを特徴とする 請求項1ないし請求項6のいずれかに記載の半導体装置 の製造方法。

【請求項8】 請求項1ないし請求項7のいずれかに記 載の半導体装置の製造方法により製造されてなることを 特徴とする半導体装置。

ることを特徴とする電子機器。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】本発明は、半導体装置および その製造方法ならびに電子機器に係り、特に半導体チッ プを複数個積層して用いるのに好適なものに関する。 [0002]

【従来の技術】半導体装置の分野においては、近年半導 体装置の小型化、軽量化を目的として、単一のパッケー ジ内に複数の半導体チップを設ける、特に各半導体チッ プを積層状態に設けるものが多く開発されてきた。この ような半導体装置は、マルチチップパッケージ(MC P)、またはマルチチップモジュール (MCM) と呼ば れている。このような装置の具体的な例としては、実開 昭62-158840号の発明が挙げられる。すなわ ち、単一のセラミック・バッケージにおいて複数のチッ

プを積層し、各チップの電極をワイヤーで接続するもの である。また、別な事例として、特開平11-1357 11号の発明のように、インターボーザと呼ばれる配線 【請求項2】 前記貫通孔内に充填する樹脂として、導 10 基板に半導体チップを実装し、インターボーザ同士を相 互に接続するとともに、積層して単一の半導体装置とす

> るものである。 [0003]

【発明が解決しようとする課題】しかしながら、実開昭 62-158840号の発明においては、半導体チップ の周囲に多数をワイヤーを配することになるので、当該 構成を有する半導体装置の容積を必要以上に大きなもの にしてしまう。また、積層される半導体チップの大きさ が略同一の場合、最上部に位置する半導体チップ以外の ものは、その電極が上位に位置する半導体チップで隠さ れた状態になるので、ボンディングが困難となる。さら に、特開平11-135711号の発明においては、略 同一の大きさの半導体チップを積層して単一の半導体装 置とすることは容易にできるが、各半導体チップをイン ターボーザに実装するとともに、インターボーザ間の電 気的接続を確保するために、実開昭62-158840 号の発明よりもはるかに複雑な製造工程を要することに なる。

【0004】そこで、本発明は、前記した従来技術の欠 30 点を解消するためになされたもので、インターボーザな どの補助的手段を用いることなく、積層された半導体チ ップと外部装置等とを電気的に接続することが可能であ るとともに、当該構成を積層される半導体チップの大き さに関係なく採用できる半導体装置およびその製造方法 ならびに電子機器を提供することを目的としている。 [0005]

【課題を解決するための手段】そこで、本発明は、上記 の目的を達成するために、半導体チップを複数個積層し てなる半導体装置の製造方法において、複数個積層され 【請求項9】 請求項8に記載の半導体装置を備えてな 40 た前記半導体チップに貫通孔を形成する第1の工程と、 前記貫通孔の内周面上に無電解メッキにより導電膜を形 成する第2の工程と、前記貫通孔内に樹脂を充填する第 3の工程と、を少なくとも有することを特徴とするもの とした。

> 【0006】とのように構成した本発明においては、積 層された半導体チップに形成された貫通孔内部に導電手 段を設けることが簡単にできる。また、樹脂を貫通孔内 部に設けるため、導電膜自体は導通が取れる程度であれ ばよく、その内面に充填する樹脂により信頼性が高ま

50 る。さらに内部に充填する樹脂に導電粒子を含んだ樹脂

を用いることにより、電気的接続の信頼性がさらに向上

【0007】また、上記の半導体装置の製造方法におい て、前記導電膜を前記貫通孔の開口部の近傍にも形成す ることを特徴とするものとした。

【0008】 このように構成した本発明においては、貫 通孔の開□部の近傍に形成された導電膜が外部装置の配 線や端子等との電気的接続に寄与するので、当該外部装 置との電気的接続の信頼性が高まる。

【0009】また、上記の半導体装置の製造方法におい て、前記第1の工程において、前記半導体チップの能動 素子形成面に形成された電極バッドの一部を穿設するよ うに貫通孔を形成することを特徴とするものとした。

【0010】とのように構成した本発明においては、電 極パッドと導電膜とが電気的に接続されるので、貫通孔 の開口部付近に設けられた導電膜または電着樹脂に外部 装置の配線や端子等を接続すれば、当該外部装置と積層 された各半導体チップとを電気的に接続することが容易 にできる。

【0011】また、上記の半導体装置の製造方法におい 20 て、前記第1の工程と前記第2の工程との間に、前記貫 通孔の内周面に絶縁膜を形成する工程を有することを特 徴とするものとした。

【0012】 このように構成した本発明においては、積 層された各半導体チップと導電膜とが絶縁膜により絶縁 されるので、当該導電膜を当該半導体チップとの電気的 接続に無関係なコンタクトとして利用することができ

【0013】また、上記の半導体装置の製造方法におい て、前記第2の工程は、前記複数個積層された前記半導 30 体チップの、前記導電膜を形成する領域以外の領域にフ ォトレジストを設ける工程と、前記導電膜を形成する領 域に触媒核を付着させる工程と、前記複数個積層された 前記半導体チップをメッキ浴する工程と、を含むことを 特徴とするものとした。

【0014】このように構成した本発明においては、導 電膜を無電解メッキにより形成するので、貫通孔内部に 導電膜を形成することが容易にできる。

【0015】また、上記の半導体装置の製造方法におい として、電着樹脂を用いることを特徴とするものにし た。とのようにして構成した本発明においては、貫通孔 内に樹脂を選択的にかつ容易に、短時間で形成すること ができる。

【0016】さらに、半導体装置において、上記のいず れかに記載の半導体装置の製造方法により製造されてな ることを特徴とするものとした。

【0017】とのように構成した本発明においては、積 層された半導体チップ同士の電気的導通を確保するの に、ワイヤー等が不要になるので、半導体装置の小型化 50 ことが好ましい。

を図ることが容易にできる。

[0018]くわえて、電子機器において、上記の半導 体装置を備えてなることを特徴とするものとした。

【0019】このように構成した本発明においては、従 来よりも小型化された半導体装置を利用できるので、電 子機器自体の小型化を図ることが容易にできる。 [0020]

【発明の実施の形態】以下に、本発明に係る半導体装置 およびその製造方法ならびに電子機器の好適な実施の形 10 態について添付図面を参照しながら詳細に説明する。

【0021】図1は、本発明の第1の実施の形態に係る 半導体装置の概略を示す断面図である。また、図2は、 本発明の第1の実施の形態に係る半導体装置の製造工程 を説明する断面図(1)である。また、図3は、本発明 の第1の実施の形態に係る半導体装置の製造工程を説明 する断面図(2)である。また、図4は、本発明の第2 の実施の形態に係る半導体装置の概略を示す断面図であ る。また、図5は、本発明の第3の実施の形態に係る半 導体装置の概略を示す断面図である。

【0022】本発明の実施の形態に係る半導体装置つい て図1に基づいて説明する。との実施の形態に係る半導 体装置100は、半導体チップ10a、10b、10 c、10dを能動素子形成面(以下、能動面とする)を 同方向に揃えた状態で積層している。積層された半導体 チップ10a、10b、10c、10dは、これらの半 導体チップの間に介在する接着剤20a、20b、20 cによって接着されている。

【0023】また、半導体チップ10a、10b、10 c、10dには、これらを積層方向に貫通する貫通孔1 2が設けられている。貫通孔12の内周面には、導電膜 16が形成されている。導電膜16は、金(Au)によ って形成されている。なお、その形成方法については後 述する。さらに、導電膜16の端部17a、17bは、 貫通孔12から外部に露出している。くわえて、貫通孔 12内部には、樹脂18が充填されている。樹脂18は アクリル系樹脂であり、カチオン型アクリル電着樹脂を 使用し、電着方式により形成されている。

[0024]以上説明した本発明の実施の形態によれ は、半導体チップ10a、10b、10c、10dのい て、前記第3の工程において、貫通孔内に充填する樹脂 40 ずれかの面において、外部装置の端子等を電極バッド1 4 d に接続すれば、導電膜16がコンタクトとしての役 割を果たして、半導体チップ10a、10b、10c、 10 dの反対側の面に設けられた基板等への接続を行う ことができる。よって、例えば、半導体チップ10dに 形成された電極パッド14 d と導電膜16 とを電気的導 体24で接続することにより、半導体チップ10a側に 設けた図示しない外部装置と半導体チップ10dとを電 気的に接続することが可能になる。なお、電極パッド1 4 d と導電膜 1 6 との接続は、スズやスズ合金等で行う

40

[0025] なお、積層される半導体チップの個数は4個に限られるものではなく、他の個数にしても良い。また、積層される半導体チップの大きさは、それぞれ異なるものであっても良い。また、貫通孔12は、積層される各半導体チップの回路等を損なわなければ、複数個、例えばすべて電極パッドに対応して設けても良い。さらに、半導体チップ10a、10b、10c、10dの間に放熱板を設けても良い。なお、これらのことは他の実施の形態にも適用できる。

【0026】また、樹脂18は、貫通孔12を完全に充 10 填していなくても良く、外部装置の端子等と接続可能に 設けられていれば良い。また、樹脂18は、導電膜16 の端部を電気的接続に使用しない場合は17a、17b 上に設けられてあっても良い。さらに、導電膜16は、 金で形成するほかに、ニッケル (Ni)、銅 (Cu) や、ニッケルー金(Ni-Au)、ニッケル-金-銅 (Ni-Au-Cu)などの合金で形成しても良い。な お、これらのことは他の実施の形態にも適用できる。 【0027】くわえて、半導体チップ10a、10b、 10 c、10 dの能動面上には、当該能動面を保護する ための絶縁膜を設けることが好ましい。具体的には、絶 縁膜としてシリコン酸化膜(SiO<sub>2</sub>)やシリコン窒化 膜(SiN)を設けることが好適である。なお、この絶 縁膜は、半導体ウェハ製造工程中で形成される後述する ようなものを半導体ウェハ製造段階で形成すれば良い。 また、半導体ウェハを各半導体チップに分割後した設け ても良い。さらに、半導体チップ10a、10b、10 c、10dの側面や裏面に後加工、例えばポッティン グ、蒸着、トランスファーモールドなどの方法により絶 縁膜を形成しても良い。なお、これらのことは他の実施 30 の形態にも適用できる。

【0028】また、本発明の第2の実施の形態に係る半導体装置のように、半導体チップ10a、10b、10c、10dに形成された金属配線層等と導電膜16との電気的絶縁を確実なものにするために、絶縁膜22を設けることが好ましい。すなわち、図4に示すように、まず、貫通孔12の内周面に絶縁膜22を形成し、その上に導電膜16を積層して設けるものとする。このようにすれば、導電膜16と半導体チップ10a、10b、10c、10dの図示しない金属配線層との電気的絶縁を確実に図ることができる。

【0029】なお、絶縁膜22としては、シリコン酸化膜(SiO2)やシリコン窒化膜(SiN)が好適である。さらに、ボリイミドなどの有機絶縁膜を形成しても良い。なお、その形成方法は、例えば、CVD法や、半導体チップ10a、10b、10c、10dを酸素を含む高温雰囲気中で熱処理して、接続孔18の内周面に露出した部分を酸化して酸化膜を形成するなど、いずれの方法によっても良い。

【0030】次に、本発明の実施の形態に係る半導体装 50 態で積層している。電極パッド14a、14b、14

6

置の製造方法について説明する。

[0031]まず、図2(A)に示すように、半導体チップの工程を終えた半導体ウェハ40を積層状態で接着し、貫通孔を形成する部位にレーザ光を照射して貫通孔12を形成する。なお、レーザ光の照射は、能動素子を穿孔するなどの損傷を与えないように注意深く行わなければならない。

【0032】なお、貫通孔12は、ウェット法やドライ法のエッチングで設けるものとしても良い。ドライ法でエッチングする場合、レーザ光を用いる方法よりも穿孔に時間を要するが、貫通孔12の内周面の荒れが小さい。具体的な、エッチング方法としては、ウェットエッチングはKOH等のアルカリ溶液、ドライエッチングはCF→等のエッチングガスを用いた方法、プラズマを用いた方法など、シリコン加工で用いられるものを用いるようにすれば良い。

【0033】次に、図2(B)に示すように、積層された半導体チップ10a、10b、10c、10dの両面にフォトレジストを塗布してフォトレジスト膜30を設け、後工程で導電膜を設ける部分を除去する。

【0034】次に、図2(C)に示すように、積層された半導体チップ10a、10b、10c、10dの両面に金の無電解メッキを施して、導電膜16を設ける。

【0035】続けて、図3(A)に示すように、電着樹脂を用いて導電膜16上にアクリル樹脂を形成する。との時、後に外部装置と電気的接続をとる必要がある端子部分に関しては、あらかじめレジスト等で電着樹脂が形成されないようにしておく。

【0036】次に、図3(B)に示すように、電着樹脂 18が貫通孔12に充填されたら、フォトレジスト膜3 0を除去する。

【0037】以上の手順により、本発明の実施の形態に係る半導体装置を製造することができる。なお、図4に示した第2の実施の形態に係る半導体装置においては、貫通孔の形成後に、前述の方法で絶縁膜22を形成し、その後に導電膜16を形成する。また、絶縁膜22の材質によっては、その上に無電解メッキによって金属を析出させて付着するのが困難な場合がある。このような場合は、図2(C)に示す無電解メッキの工程の前に、半導体チップ10a、10b、10c、10dをパラジウムコロイド溶液に浸潤し、導電膜を形成する部位にパラジウムを付着させる処理を行う。この処理を行うと、パラジウムが触媒核となって、絶縁膜22上に導電膜を形成することが容易にできる。

【0038】次に、本発明の実施の形態に係る半導体装置について図5に基づいて説明する。この実施の形態に係る半導体装置100は、半導体チップ10a、10b、10c、10dを、それぞれの電極バッド14a、14b、14c、14dを設けた面を同方向に揃えた状態で積層している。電極バッド14a、14b、14

c、14dは、それぞれ半導体チップ10a、10b. 10 c、10 d に形成された図示しない回路に接続され ている。なお、接着剤10a、10b、10c、導電膜 16および樹脂18は、第1の実施の形態に係るものと 同じ構成であり、樹脂18はアクリル系電着樹脂を使用 している。

【0039】以上説明した本発明の実施の形態によれ ば、外部装置の端子等を導電膜16の端部17a、17 bのいずれかに接続すれば、導電膜16を介して半導体 チップ10a、10b、10c、10dの電極パッド1 10 体装置のコストダウンにも著しく寄与する。 4a、14b、14c、14dと接続されることにな る。よって、積層される半導体チップの大きさに関係な く、積層された半導体チップと外部装置とを電気的に接 続することができる。また、インターボーザのような補 助的手段を必要としない。

【0040】なお、電極パッド14a、14b、14c と導電膜16との電気的導通を確実に確保するために、 電極パッド14a、14b、14c上にスズやスズ系合 金などの導電材を設け、電極パッド14a、14b、1 4 c に併せて導電膜 1 6 とこの導電材とが接続されるよ 20 うにしても良い。さらに、電極パッド14a、14b、 14c、14dは、アルミニウム(A1)、アルミニウ ムーシリコン(Al-Si)、銅(Cu)、アルミニウ ムーシリコンー銅(Al-Si-Cu)など一般的に半 導体チップの電極や配線として用いられているものであ れば、どのような材質のものであっても良い。さらに、 電極パッド14 d上に、導電膜16がとの接続が安定的 に行えるように、一般的にアンダーバンプメタルとして 知られているような金属層(例えば、Ti-W、Pt-Au、Ni、Cu-Auなど)を形成するようにすると 30 とが好ましい。

【0041】以上述べたように、本発明の各実施の形態 に係る半導体装置100は、その内部を貫通して周辺装 置の電気的接続を図ることが可能であり、ワイヤーやイ ンターボーザ等を用いる必要がない。また、ワイヤーや インターボーザ等を設けない分だけ用い半導体装置の実 装面積の縮小化を図ることができるので、この半導体装 置100を電子機器に実装すれば電気機器自体の小型化 を図ることができる。

## [0042]

【発明の効果】以上に説明したように、本発明によれ ば、半導体チップを複数個積層してなる半導体装置の製 造方法において、複数個積層された前記半導体チップに 貫通孔を形成する第1の工程と、前記貫通孔の内周面上 に無電解メッキにより導電膜を形成する第2の工程と、 前記貫通孔内に導電性のある樹脂を設ける第3の工程 と、を少なくとも有する構成としているため、積層され た半導体チップの貫通孔を介して半導体チップ同士や、 半導体チップとの外部装置とを電気的に接続することが できる。また、ワイヤーやインターポーザ等の補助的手 段を介することなく、電気的な接続を行うことができる ので、半導体装置の小型化にも寄与するとともに、半導

#### 【図面の簡単な説明】

【図1】本発明の第1の実施の形態に係る半導体装置の 概略を示す断面図である。

【図2】本発明の第1の実施の形態に係る半導体装置の 製造工程を説明する断面図(1)である。

【図3】本発明の第1の実施の形態に係る半導体装置の 製造工程を説明する断面図(2)である。

【図4】本発明の第2の実施の形態に係る半導体装置の 概略を示す断面図である。

【図5】本発明の第3の実施の形態に係る半導体装置の 概略を示す断面図である。

### 【符号の説明】

| 1 | n s | 半導体チップ             | • |

|---|-----|--------------------|---|

| 1 | US  | !―――――――――――――― ツッ | , |

### 12 …… 貫通孔

14a……電極パッド

14b……電極パッド

14 c……電極パッド

14 d……電極パッド

16 ……導電膜

17a……端部

17b……端部

18 .....電着樹脂

20 a ……接着剤

20b……接着剤

20 c ······接着剤 22……絶縁膜

40 24 ……電気的導体

30……フォトレジスト膜

40 …… 積層した半導体ウェハ

100……半導体装置

10a

17b 12